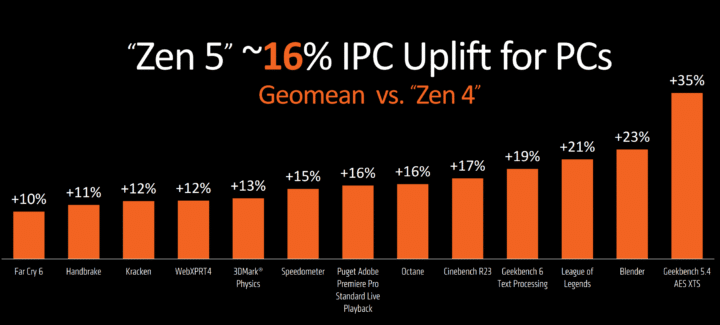

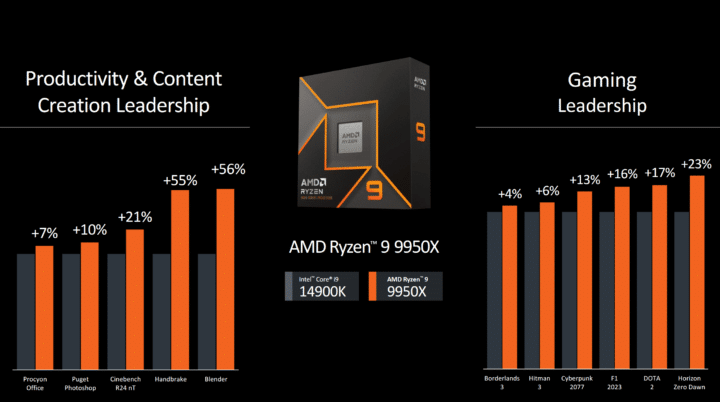

AMD’s next-gen Ryzen 9000 processors are official, with concrete specs and a launch date. The Zen 5 desktop family is scheduled to launch in July (next month), with an upgraded frontend, wider memory subsystem, and improved AVX512 bandwidth. The chipmaker claims an average IPC increase of 16%, with the highest gains in Blender, Cinebench R23, League of Legends, and other content creation workloads. So, what has changed with Zen 5, and were the leaks accurate?

The core counts of the Ryzen 9000 family are unchanged, so most of that section was on point. However, the CPU boost clocks are unchanged, and we still don’t have official confirmation on the L1/L2 cache. The overall cache on the Ryzen 9 9950X is 80 MB, the same as the 7950X, but this doesn’t include the L1I and L1D cache.

According to rumors, Zen 5 will expand the L1D cache from 32KB to 48KB (12-way) with a 4-cycle load, complemented by an expanded Data Translation Buffer and a recalibrated branch predictor. The L1I cache will likely remain unchanged at 32KB (8-way).

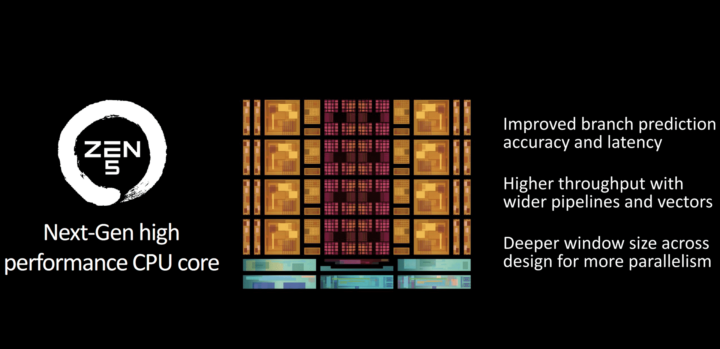

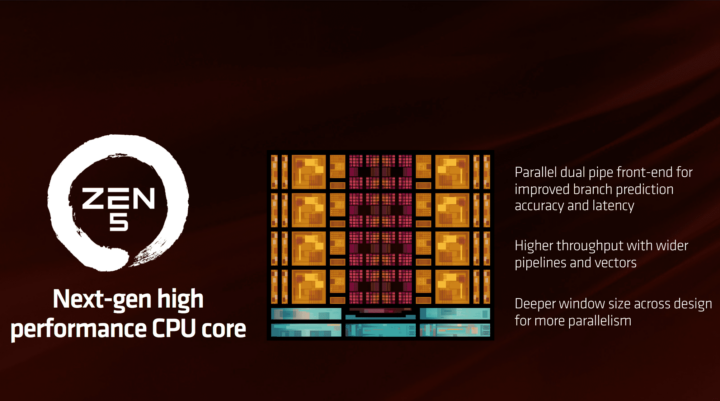

The branch predictor has been upgraded with “improved prediction accuracy and latency.” Per rumors, Zen 5’s branch predictor executes “Zero bubble” conditional branches. This implies that conditional branches are taken without interrupting or stalling the pipeline.

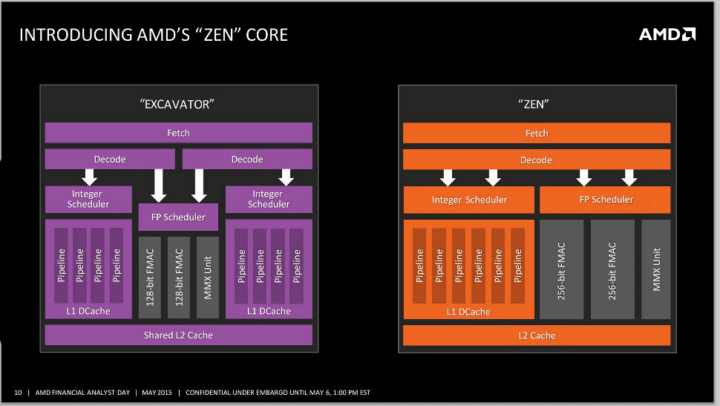

The decoder looks unchanged (4-way) with a 2-basic block fetch. The rename/dispatch buffer has been consolidated to simultaneously process up to 8 micro-ops (previously 6) with support for op-fusion. This allows two micro-ops from the same instruction to be treated as one at some points in the pipeline, doubling the effective throughput.

The Dispatch will also be upgraded from 6 maco-ops on Zen 4 to 8 macro-ops on Zen 5, keeping the backend fed at all times. This implies the 2x instruction bandwidth for frontend instructions and makes me wonder if the decoder will be expanded. Then, there’s the above slide.

A parallel dual pipe front-end for improved branch prediction accuracy and latency. This complements the above point on branch prediction, but what does the dual front-end stand for? Reminds you of the Excavator (Bulldozer) frontend, except with Zen 5, we’re looking at two frontend pipes per core rather than a module of two cores. Has the decoder width changed as well?

There’s mention of wider pipelines and vectors which likely means wider execution bandwidth. On the integer side, the instruction scheduler has allegedly been reinforced into a unified queue with “larger structure sizes.” Multiple smaller scheduler windows have been consolidated into larger queues.

The integer ALU count has been increased to 6 (previously 4) to accommodate the higher throughput. A fourth AGU (Address Generation Unit) has also been added to keep the load-store queues fed. Overall, we’ve got 10 execution ports on Zen 5’s Integer backend. The Load/Store bandwidth has been expanded to 4 loads (previously 3) or two stores per cycle. This accounts for the increased L1 to L2 bandwidth, and the L1 to FP bandwidth.

On the Floating Point end, all four execution ports have (reportedly) been doubled in width to 512-bit to support AVX-512 instructions. A fifth port consisting of two 256-bit units has also been added. The expanded EUs mean larger floating point registers to sustain them, substantially larger. I believe this will only be implemented for the Epyc cores, while client Zen 5 will get the fifth FP port (256b).

The gains (over the Intel Core i9-14900) in gaming workloads vary from 4% in Borderlands to 23% in Horizon Zero Dawn. These are likely the result of an upgraded core interconnect (Ladder as per AdoredTV). Although the frontend and backend improvements also contribute to this, I believe the interconnect plays a vital role.

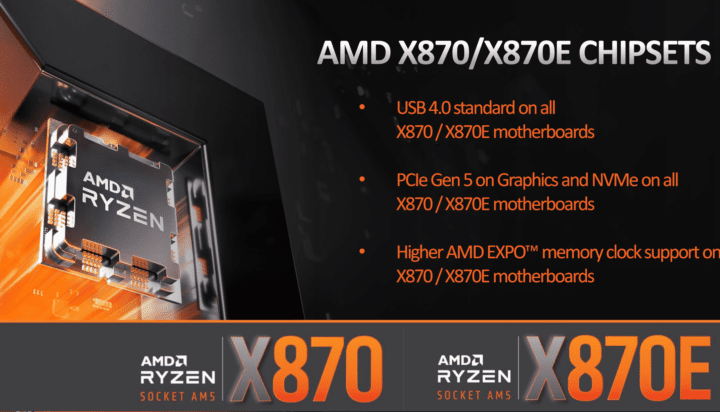

The X870/X870E chipsets aren’t all that different from X670/X670E. All dGPU and M.2 SSD slots (up to 24) have been upgraded to PCIe Gen 5. X670E boards already feature up to 24 PCIe Gen 5 lanes. The main difference can be seen on the X870 chipset which has been upgraded to sport up to 24 PCIe Gen 5 lanes, up from just 8x on X670.

| CPU PCIe Lanes | Chipset Lanes | |||||||||

| GRAPHICS | NVMe | USABLE PCIe/PCIe 5.0 | CPU OVERCLOCKING | DDR5 MEMORY OVERCLOCKING/ AMD EXPO | USB 5Gbps | USB 10Gbps | USB 20Gbps | SATA PORTS (OR PCIe 3.0) | USB 4.0 | |

| X870E | 1×16 or 2×8 PCIe 5.0 | 1×4 PCIe 5.0+4x PCIe GPP | 44/24 | Yes | Yes | 2 | 12 | 2 | 8 | STANDARD |

| X870 | 1×16 or 2×8 PCIe 5.0 | 1×4 PCIe 5.0+4x PCIe GPP | 36/24 | Yes | Yes | 1 | 6 | 1 | 4 | STANDARD |

| X670E | 1×16 or 2×8 PCIe 5.0 | 1×4 PCIe 5.0+4x PCIe GPP | 44/24 | Yes | Yes | 2 | 12 | 2 | 8 | optional |

| X670 | 1×16 or 2×8 PCIe 4.0 | 1×4 PCIe 5.0+4x PCIe GPP | 44/8 | Yes | Yes | 2 | 12 | 2 | 8 | optional |

| B650E | 1×16 or 2×8 PCIe 5.0 | 1×4 PCIe 5.0+4x PCIe GPP | 36/24 | Yes | Yes | 1 | 6 | 1 | 4 | optional |

| B650 | 1×16 or 2×8 PCIe 4.0 | 1×4 PCIe 4.0 (or PCIe 5.0) | 36/0 | Yes | Yes | 1 | 6 | 1 | 4 | optional |

| A620/A620A | 1×16 PCIe 4.0 | 1×4 PCIe 4.0 | 32/0 | No | Yes | 2 | 2 | – | 4 | optional |

| PRO 665 | 1×16 or 2×8 | 1×4 PCIe 4.0 (or PCIe 5.0) | 36/0 | No | No | 1 | 6 | 1 | 4 | optional |

| PCIe 4.0 | ||||||||||

| PRO 600 | 1×16 or 2×8 | 1×4 PCIe 4.0+4x PCIe GPP | 28/0 | No | No | 0 | 0 | 0 | 0 | optional |

| PCIe 4.0 | ||||||||||

AMD Ryzen 9000X3D and Zen 5 V-Cache

According to Kepler, the Ryzen 9000X3D processors (Zen 5 3D V-Cache) will be revealed during CES 2025, slated to be held in the first week of January 2025. If the Ryzen 9000 “Zen 5” CPUs launch between summer and fall (June to September), then a 6-month gap separating them from the 3D V-Cache variants makes sense. This will depend on when Intel launches its 15th Gen Arrow Lake processors. They’ll have a similar effect on the market as Raptor Lake.

Frequently Asked Questions

- Will the Ryzen 9000 CPUs be compatible with existing AM5 motherboards (A620/B650/B650E/X670/X670E)?

AMD has officially confirmed that the AM5 socket will be supported through 2025. At the very least, the existing 600-series motherboards will be fully compatible with the Ryzen 9000 CPUs. Some board partners have already released firmware enabling support for the next-gen Zen 5 processors.

You’ll also have the option to buy the 800-series motherboards which will feature increased I/O options on non-X SKUs.

- When will the Ryzen 9000 CPUs be available for purchase?

The Ryzen 9000 CPUs will be available for purchase in July 2024.

- How fast will the Ryzen 9000 CPUs be compared to the 7000 series and Intel’s Raptor Lake offering?

According to AMD, the Zen 5 core offers an average 16% IPC uplift. The gains in individual applications range from 10-35%, with content creation workloads benefiting heavily.

Further reading: AMD Zen 5 Strix Point/Halo, Granite Ridge & Turin: Ryzen 9000 Specs, News & Rumors